in my last post, i established that the CP2114 doesn't work. so how are we going to solve the synchronous clocking problem, and build a working digital input for the DSP 01?

there's always the brute-force approach - use a high-fidelity asynchronous sample-rate converter. this is a circuit which doesn't care what sample rate (and sample clock) the source is using - it will resample the signal to match the DSP 01's internal clock. after more internet research, i decided to use the CS8422.

the CS8422 is a 24-bit Asynchronous Stereo Sample-Rate Converter. it will accept a digital audio signal at almost any sample rate and resample it to exactly match the DSP 01's fixed 48kHz sample clock. while the CP2114 has a USB input, the CS8422 uses SPDIF, which i have certainly played with before.

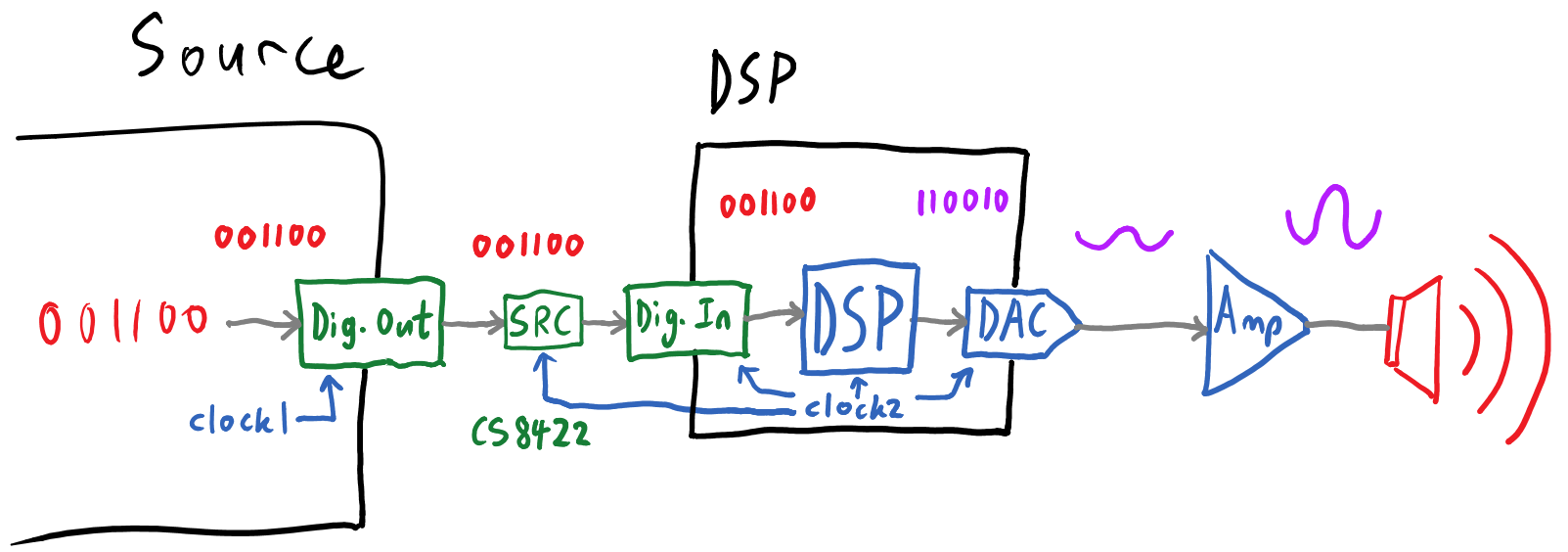

so here's what we've got:

now the digital input should be resampled to match the DSP 01's internal clock (clock2), but does it really work? let's build a board to connect them!

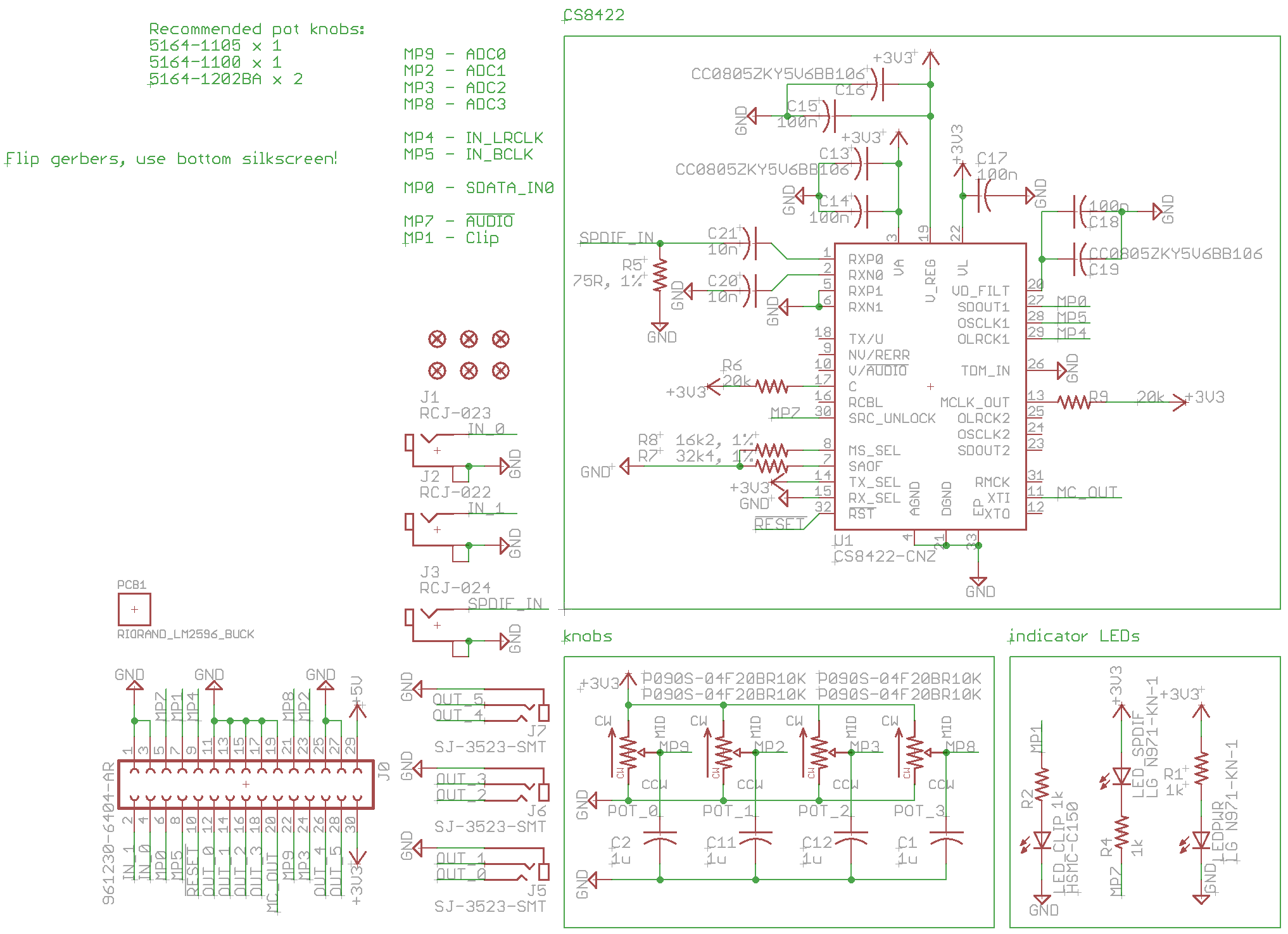

PCB layout: front (left) and back (right)

..i didn't even take a photo of that one. but whatever, it worked. which allowed me to make a much better one, as you shall see.

time and time again, i have found that connectors are the bane of my existence. they're bulky, expensive, ugly and time-consuming. even the first DSP 01 project used 3.5mm-to-RCA audio cables & connectors for internal hook-up, and that doubled the size of the chassis. how could i entirely purge ugly internal connectors from my next project?

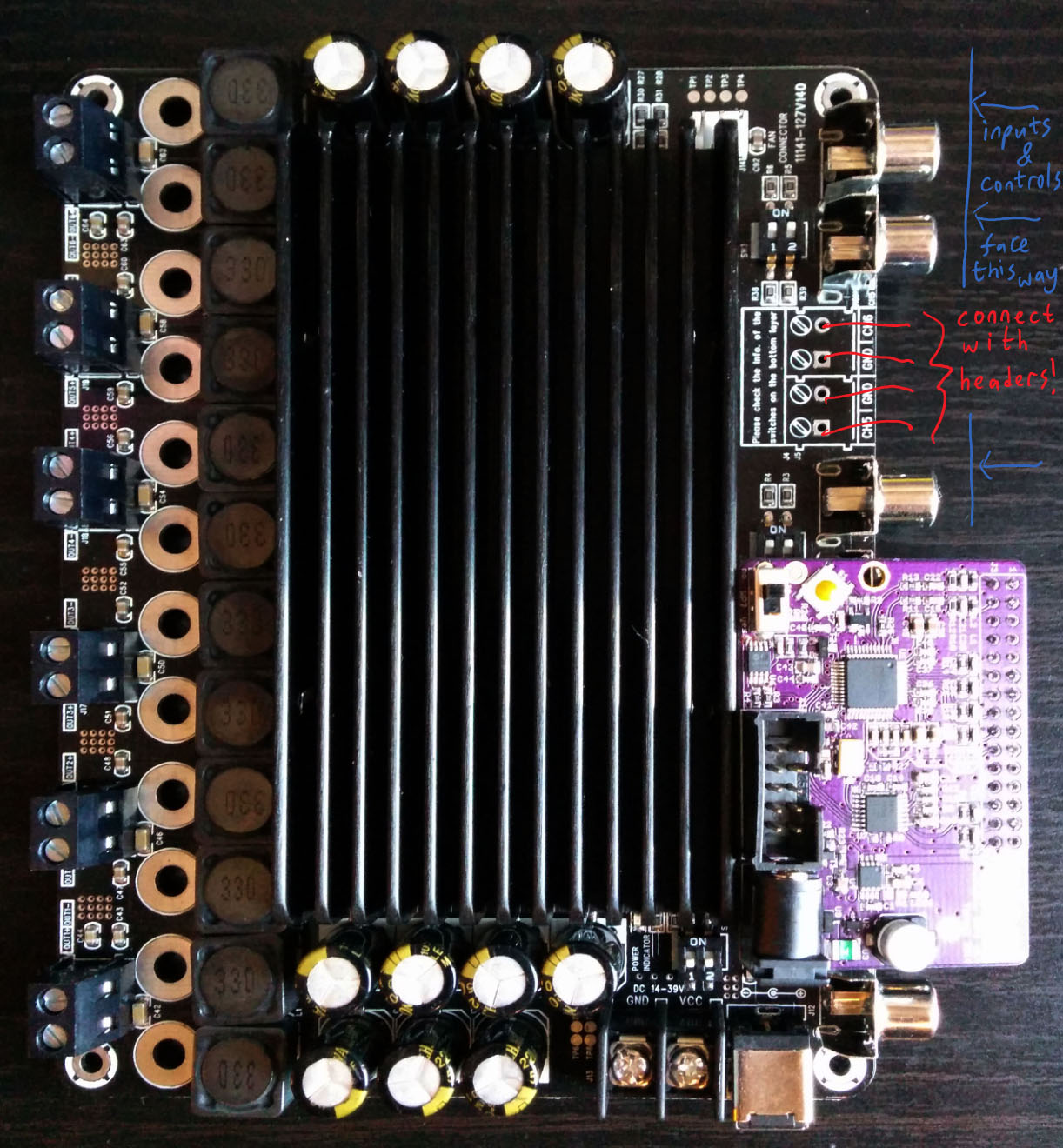

the objective - to connect a DSP 01 board to a 6-channel power amplifier and a front-facing instrument panel. instead of RCA jacks, i'd link everything with 0.1" headers. they would go together like this:

the amplifier & DSP 01 would connect to a horizontal backplate, but the controls & inputs needed a vertical front panel. i'd have to build two boards and connect them at right-angles.

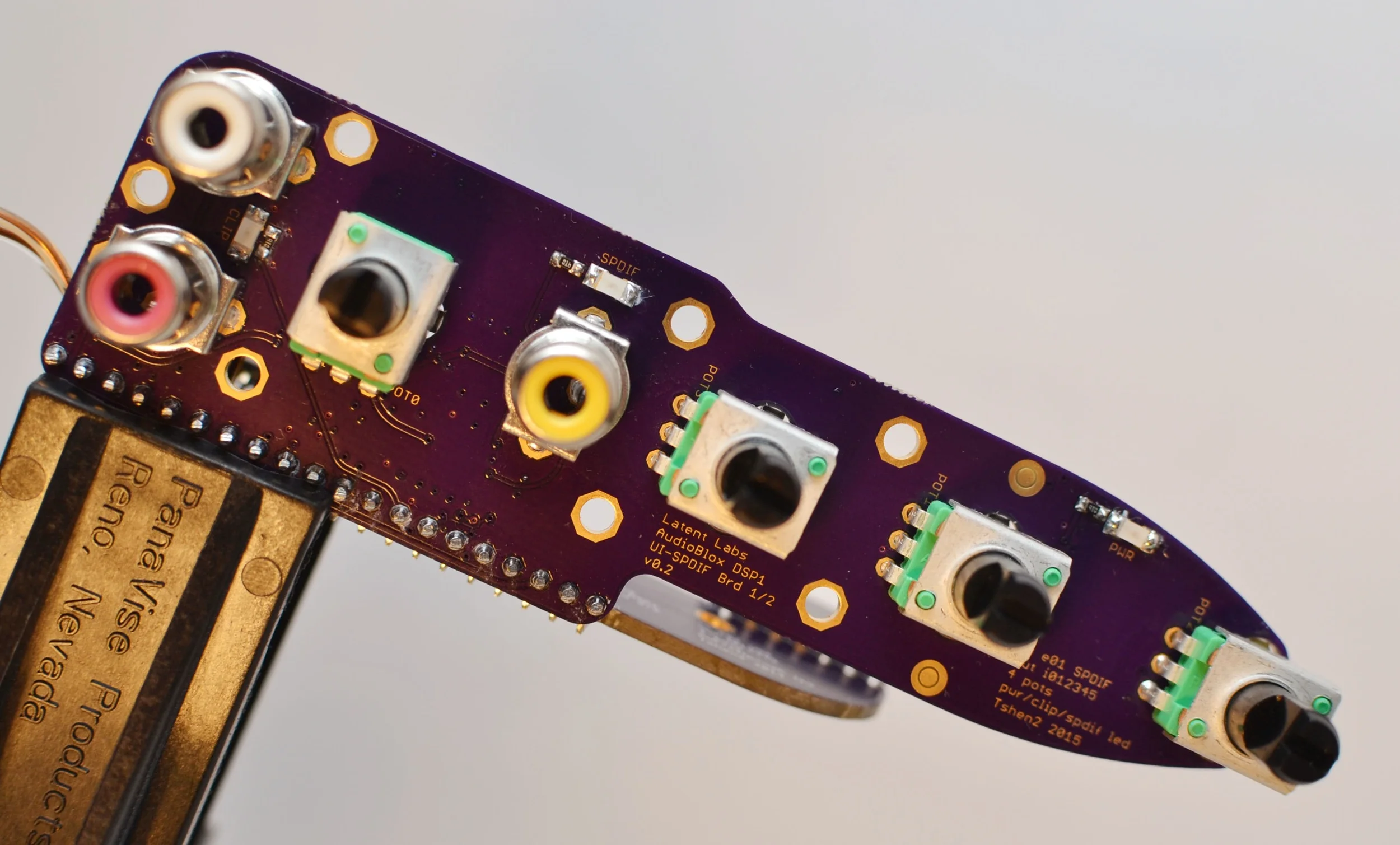

time for 3D PCBs!

PCB layout: control panel front (upper) & back (center), orthogonal backplate (lower).

the small box on the left is a 5V switching regulator. this lets the DSP 01 run on the same 24V supply voltage as the 6-channel amplifier.

and now to put it together.

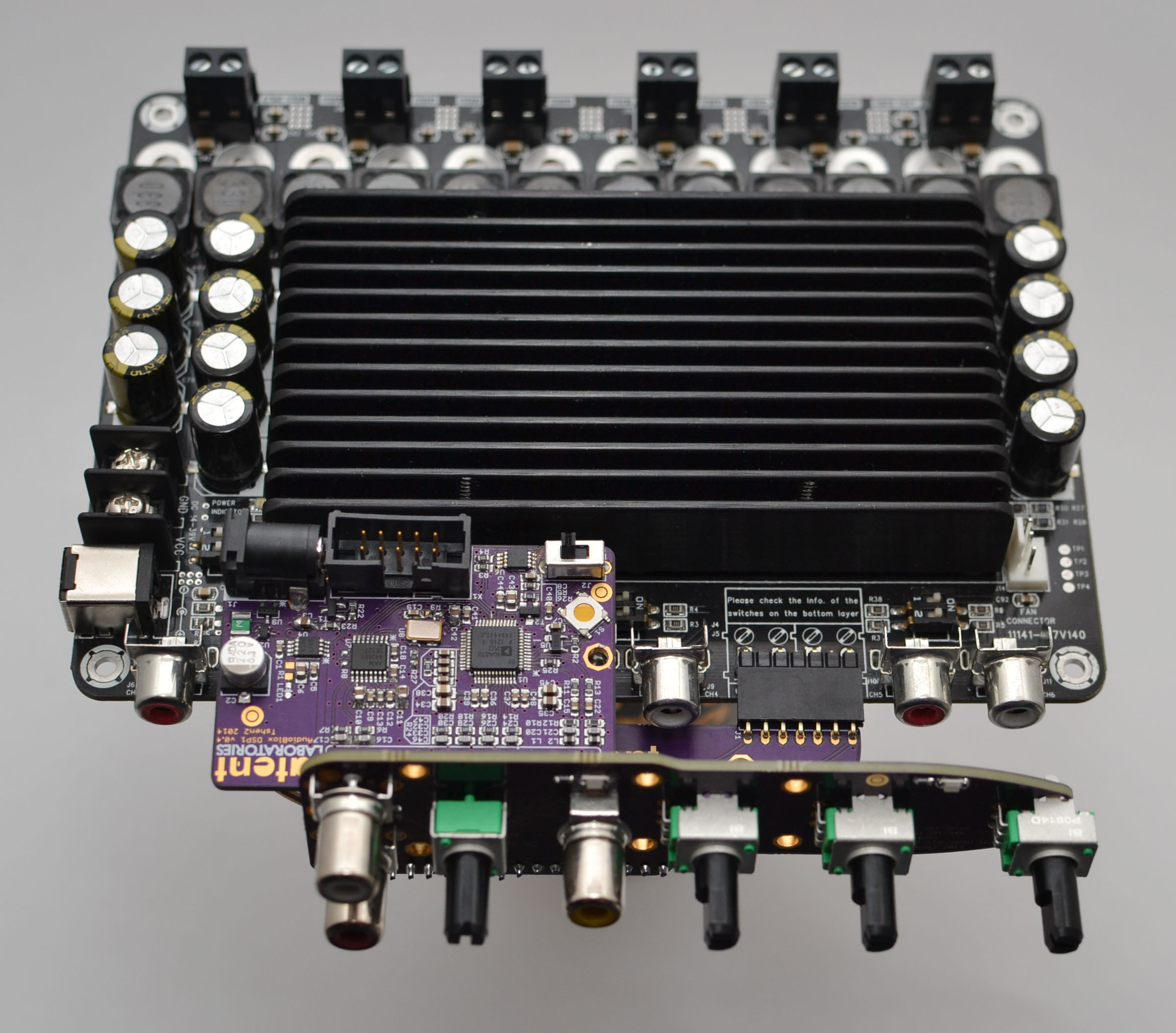

i think it's quite pretty.

next update: a moment of art & industrial design.

Tshen2 2015